# Systèmes Embarqués et Hétérogènes

TAF SEH (22B)

Trois UE cœur pour vous offrir une base solide...

Former des ingénieurs capables de sélectionner, concevoir et réaliser les systèmes embarqués intelligents de demain!

## Responsable

Stefan Weithoffer

## Mots-clés

Systèmes embarqués, Accélération de calcul, VHDL, ASIC, FPGA, GPU, Processeurs, Circuits numériques, Logiciel/matière, Adéquation algorithme/ architecture, Systèmes d'exploitation, Calcul parallèle, Intelligence artificielle, Optimisation

## UE Electives (Crenaux D)

Choix libre – parmi les UEs offertes sur le campus Brest.

## UE Electives (Crenaux E)

Choix libre – parmi les UEs offertes sur le campus Brest.

GRENOB - Workshop à Grenoble – recherche et industrie des micro et nanotechnologies

## Enjeux de la TAF SEH en bloc de compétences

**BC01** – Manager un projet, un système embarqué hétérogène en anticipant les évolutions technologiques et en intégrant des pratiques d'amélioration continue pour optimiser les performances et/ou la consommation énergétique.

**BC02** – Contribuer activement à un collectif au sein d'une équipe multidisciplinaire et potentiellement interculturel, pour concevoir et déployer des architectures embarquées, en adoptant une approche d'écoute active et en proposant des solutions adaptées aux contraintes matérielles et logicielles.

**BC03** – Élaborer un diagnostic en analysant les défis liés à l'intégration de systèmes hétérogènes sur puce en identifiant les verrous en enjeux technologiques (énergétiques, temps réel et de sécurité...)

**BC04** – Concevoir une solution à un problème en proposant une architecture embarquée innovante en intégrant les contraintes de performances, de consommation énergétique et de scalabilité, tout en anticipant les évolutions des technologies de semi-conducteurs.

**BC06** – Produire, mettre en place et maintenir en service, sur la base de spécifications techniques dans le domaine des systèmes embarqués, en justifiant les choix effectués et en garantissant la fiabilité et/ou une faible consommation énergétique.

## Site

Campus Brest

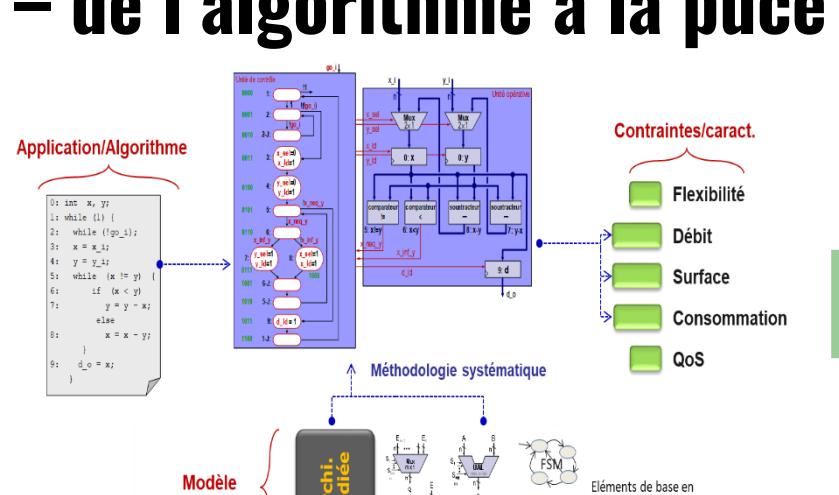

### UE A: Méthodologies de conception – de l'algorithme à la puce (PUCE)

Méthodologies de conception de circuits numériques performants à partir d'une description algorithmique et d'un ensemble de contraintes.

### UE B: Systèmes embarqués – interaction logiciel/matériel (SEIML)

Interaction entre logiciel et matériel dans les systèmes embarqués. Processeurs, mémoires, bus de comm., périphériques. Linux embarqué, pilotes, tâches.

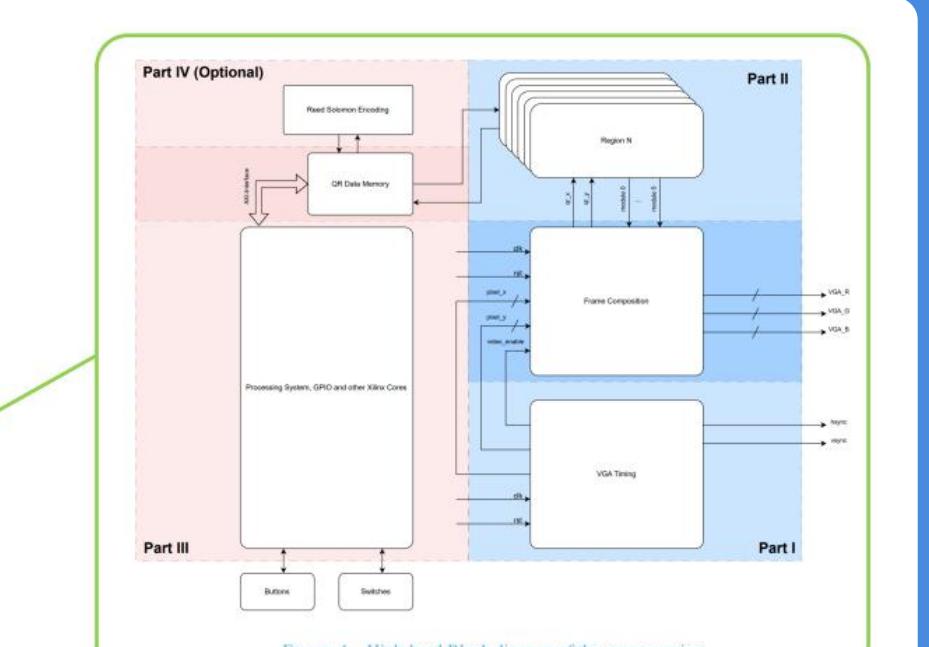

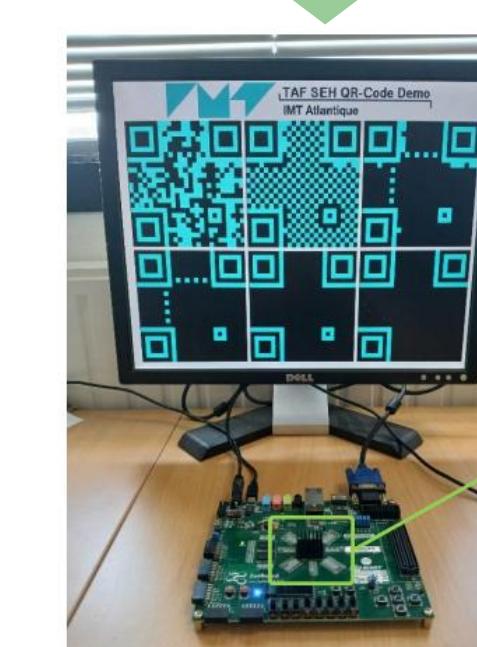

### UE C: Systèmes embarqués – projet : conception, test et implémentation (SECTI)

L'objectif de ce cours est de réaliser une plateforme de démonstration pour l'encodage de QR-codes. Il s'appuie sur les compétences acquises dans les cours PUCE et SEIML et les met en pratique dans un contexte de projet.

Le système à concevoir et à implémenter comprend une application s'exécutant sur le cœur ARM embarqué du dispositif Zynq, ainsi qu'un coprocesseur facilitant l'encodage des QR-codes et la logique d'interface avec un affichage VGA.

Au sein de la TAF, choisissez parmi trois parcours....

### Parcours I: Digital Design of Embedded Systems

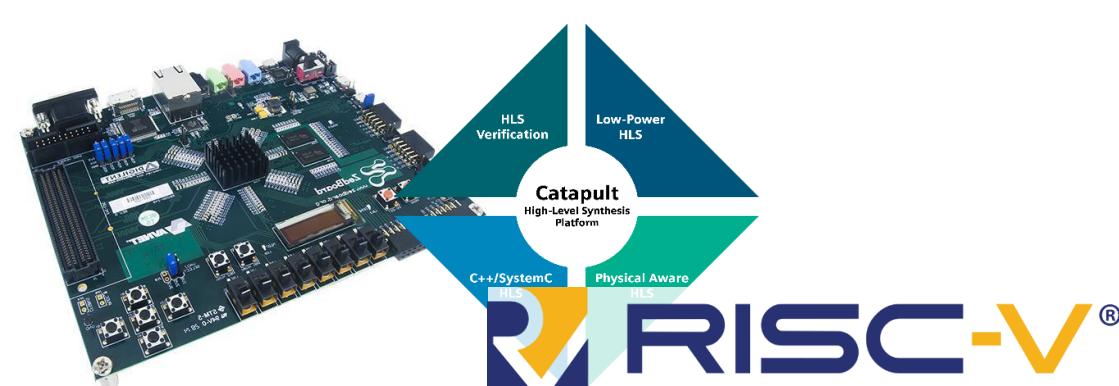

**ARISE:** Architectures RISC-V et extensions de jeu d'instructions

Introduction et approfondissement des concepts en architecture de processeurs modernes avec un focus sur les aspects théoriques et pratiques de l'ISA RISC-V.

**AIRV:** Accélération IA sur RISC-V

Apprenez à identifier les goulots d'étranglement et à concevoir des accélérateurs IA efficaces pour les plateformes RISC-V en appliquant les principes de co-conception logiciel-matériel, à la fois théoriques et pratiques.

**CHLS:** Conception haut niveau de circuits

Méthodes de conception haut niveau (SystemC, C++ HLS, ASIP) pour accélérer le développement, avec une expérience pratique sur des outils industriels tels que Tensilica, Vivado HLS et Catapult.

### Parcours II: Artificial Intelligence & HPC

**PARPING:** Calcul Parallèle pour l'ingénieur

Accélération des calculs par le parallélisme, en exploitant les techniques ILP (Instruction-Level), DLP (Data-Level), TLP (Thread-Level), NLP (Node-Level), ainsi que les architectures GPU.

**EFFDL:** Deep Learning efficace

Conception de réseaux neuronaux efficaces pour des systèmes à ressources limitées, en utilisant des techniques telles que la quantification, l'élagage, la distillation et la factorisation.

**PML:** Projects on Recent Advances in Machine Learning

Exploration des sujets récents en recherche ML/IA, analyse de publications scientifiques, et présentation de résultats théoriques et expérimentaux.

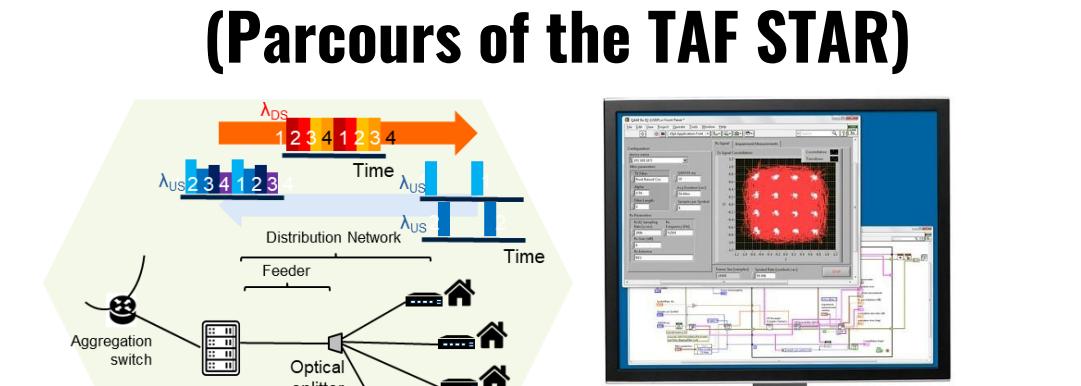

### Parcours III: Telecommunication (Parcours de la TAF STAR)

**RCNUM:** Récepteurs pour communications numériques

Méthodologie de conception, de validation théorique et expérimentale de récepteurs pour communications numériques.

**REMOB:** Réseaux Mobiles

Étude des réseaux mobiles (4G, 5G/5G+, WiFi), des transmissions mono- et multi-antennes, et des canaux sans fil, avec travaux pratiques sur modulation et conception radio

**RESOPT:** ARCHITECTURES ET réseaux OPTIQUES

Étude de l'infrastructure optique et de ses aspects techniques, économiques et réglementaires, avec mini-projets sur dimensionnement, techno-éco et conception d'offres

Combinez la TAF SEH avec une autre TAF en 2<sup>e</sup> / 3<sup>e</sup> année...

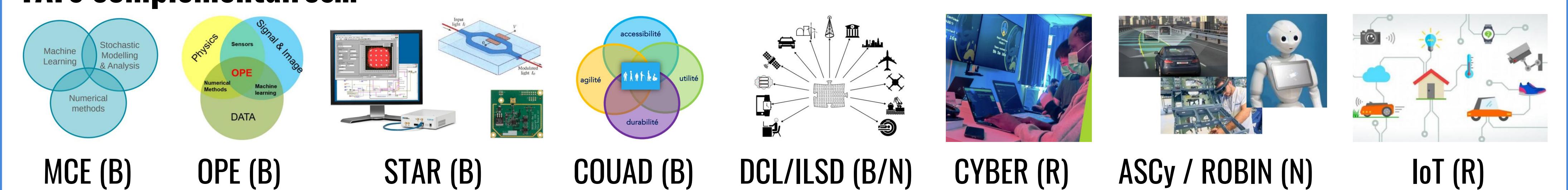

### TAFs complémentaires...

### Devenez...

Engineering Program Analyst chez Intel pour gérer des projets de conception de SoC, en liaison avec un responsable de programme, un responsable technique et des équipes transverses.

Comme Varenka Martin.

Senior Hardware Designer chez STMicroelectronics pour gérer la conception, l'optimisation et la vérification de nouveaux IP numériques intégrés aux microcontrôleurs.

Comme Sandrine Coudière.

FPGA Tech Lead chez OVH pour développer des solutions originales combinant matériel, logiciel et réseau.

Comme Tristan Groléat.

Security Architecture Director chez Qualcomm, après des postes de CTO et VP R&D at TrustAZUR, ingénieur puis directeur R&D chez Texas Instruments, Samsung et Inside Secure sur la sécurité des systèmes embarqués.

Comme Aymeric Vial.

Réalisez votre projet professionnel....

### Entreprises cibles...

- Transports (automobile, aéronautique, aérospatial)

- Électronique grand public

- Télécoms et IoT

- Robotique et Domotique

- Défense

- Cyber-sécurité

- Santé